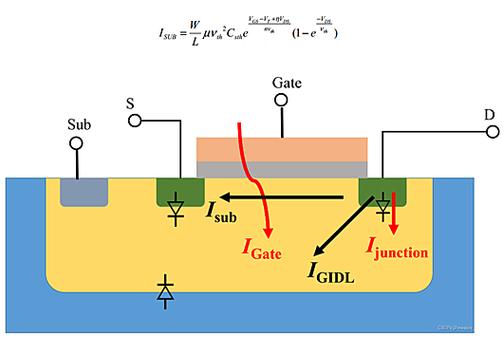

那么,本日我们来理解MOS管以下5种泄电流。

反偏结泄露电流

:当MOS管关断时,通过反偏二极管从源货漏极到衬底。

其紧张由两部分组成:

由耗尽区边缘的扩散和漂移电流产生由耗尽区中的产生的电子-空穴对形成在一些重掺杂的PN区,还会携带一些间隧穿(BTBT)征象贡献的泄露电流。不过源漏二极管和阱二极管的结反向偏置透露电流分量,相对付其他三个泄露分量险些可以忽略不计。

栅极致漏极泄露电流

栅极致漏极泄露电流一样平常由MOS管漏极结中的高场效应引起的。由于源极和漏綦重叠区域之间存在大电场而发生隧穿(包含雪崩隧穿和BTBT隧穿),产生了 电子-空穴对。由于电子被扫入阱中,空穴积累在楼中形成/GIDL。

栅极与漏綦重叠区域下的强电场,会导致深度耗尽区,以及使漏极和阱交界处耗尽层变薄,因而有效形成漏极到阱的电流/GIDL。/GIDL与VGD有关,一样平常NMOS的/GIDL会比PMOS的大两个数量级。

栅极直接隧穿电流

栅极泄露电流是由栅极上的电荷隧穿过栅氧化层进入阱(衬底)中形成。一样平常栅氧化层厚度在3-4nm,由于在栅氧化物层上施加高电场,电子通过Fowler-Nordheim隧道进入氧化物层的导带而产生的/G。

随着晶体管长度和电源电压的减小,栅极氧化物的厚度也必须减小,以坚持对沟道区域的有效栅极掌握。不幸的是,由于电子的直接隧穿会导致栅极泄露呈指数级增加。

目前可以利用高K介电材料(如TiO2和Ta2O5),替代SiO2作为栅极绝缘体介质层。

这种方法可以战胜栅极泄电流,并同时对其栅极保持良好的掌握。

亚阈值泄露电流

:指沟道处于弱反型状态下的源泄电流,是由器件沟道少数载流子的扩散电流引起的。当栅源电压低于阈值电压Vth时,器件不会立时关闭,而是进入了“亚阈值区”而IDS成了VGS的指数函数。

在目前的CMOS技能中,亚阈值泄露电流ISUB会比其他泄露电流分量大得多。这紧张是由于当代CMOS器件中的VT相对较低。

隧穿栅极氧化层泄电流

在短沟道器件中,薄栅极氧化物会在 SiO2 层上产生高电场。由于高电场浸染,低氧化物厚度会导致电子从衬底隧穿到栅极,同时从栅极通过栅极氧化物,隧穿到衬底,进而形成栅极氧化物的隧穿电流。

(a)是一个平带 MOS 晶体管,即个中不存在电荷。

当栅极度子正偏置时,能带图会发生变革,如图(b)。强烈反转表面处的电子隧道进入或穿过 SiO 2层,从而产生栅极电流。

另一方面,当施加负栅极电压时,来自 n+ 多晶硅栅极的电子隧道进入或穿过 SiO 2层,从而产生栅极电流,如图 (c) 所示。