电路事理图的EMC风险评估(剖析)是建立在对事理图中的电路进行划分的根本上 的,通过剖析将电路事理图分成:

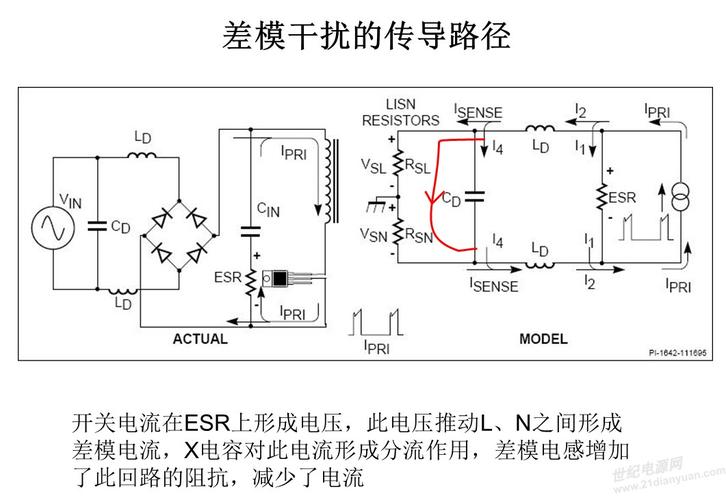

“脏”的部分“干净”的部分滤波、去耦的部分须要做分外处理的部分电路事理图的EMC风险评估(剖析)事理,个中“脏”或噪声区域部 分常日是电路中的I/O部分或产品的壳体。在这些I/。端口或壳体上须要进行EMC测 试,EMC滋扰须要从这些I/O 口注入,这些电路是产品中受滋扰最严重、最直接的部 分。如产品的ESD放电点、电源端口的电路,通信端口的电路,其他输入/输岀口的电路。常日,这些电路不能直接延伸到内部干净的电路区域,其间须要包含至少具有一个以 上器件(如电容)组成的滤波器或滤波电路与其合营利用,滤波电路包括共模滤波和差模 滤波。对付接地产品,共模滤波是必须的。在有些不能利用共模滤波的情形下(如产品浮 地),除了 I/O端口须要进行差模滤波外,还要在PCB设计时担保共模电流滋扰路径上地 平面的完全,以降落共模电流流过期产生的压降,不然就须要在地阻抗较高区域的旗子暗记线 上加电容进行差模滤波。

“干净”区域的电路部分是不会受外接直接滋扰或内部噪声源滋扰的部分电路。在 电路中其常日位于滤波电路之后,也是电路中须要保护的部分,如A/D -D/A转换电路、检测电路、CPU核心电路等。滤波、去耦及隔离区域部分是介于“干净”电路部分与“脏”电路部分之间的、完成 对“干净"电路和“脏”电路隔离的电容或其他PCB设计方法,它是为了保护“干净” 的电路不受外界滋扰的影响,并将滋扰滤除,或将产品内部分外噪声电路或敏感电路“隔 离”在其他电路之外。滤波电路常日至少由一个或多个电容组成,每每还会包括电感、磁 珠、电阻等器件。

内部噪声电路、敏感电路的区域是一些须要做分外处理的部分,它是电路中比较分外的部分。常日分外电路包括两种电路,第一种是极其敏感的电路(如复位电路、低电压、 低电流检测电路、低电压仿照电路、高输入阻抗电路等),这些电路不像其他普通数字电 路一样具有相对较高的抗滋扰能力。对付这些敏感电路,除了进行像普通电路一样滤波去 耦处理之外,还有必要进行一些额外处理,如二级滤波、屏蔽、对其旗子暗记线进行包地等处 理。第二种是内部电路的噪声源(如电路中的晶振和时钟电路,开关电源中的开关管、开 关回路)。由辐射形成事理的描述可知,形成辐射的必要条件是辐射噪声源与天线。对这部分电路的处理紧张是为了降落噪声源的电平,并将其隔离于“天线”之外, 常日须要做分外处理,常用的方法有屏蔽、去耦、对其旗子暗记线进行包地等,使其与其他信 号线和电路之间不发生串扰,以免噪声传输繁芜化。

在PCB布线布局的时候,各个电路部分之间的串扰是着重须要考虑的,避免串扰的方法,在后续文章中进行描述。

该内容转载自硬件设计技能,仅供学习互换利用,如有侵权,请联系删除。