什么是“摩尔定律”?

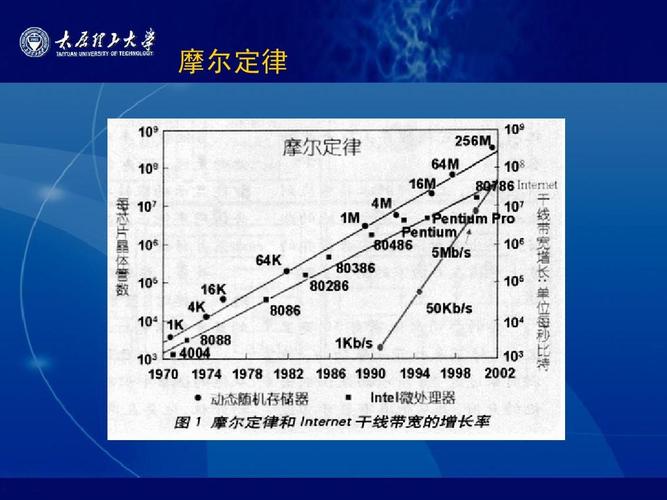

摩尔定律因此英特尔联合创始人戈登·摩尔(Gordon Moore)的名字命名的。戈登·摩尔在1965年时提出,半导体芯片上集成的晶体管和电阻数量将每年增加一倍。1975年,他又根据当时的实际情形对摩尔定律进行了改动,把\"大众每年增加一倍\"大众改为了\"大众每18到24个月增加一倍\"大众。

摩尔定律发展至今已有50多年,在这50多年间,不断有人唱衰,乃至有人提出“摩尔定律已去世”的不雅观点。

芯片制造商已经利用了各种手段来跟上摩尔定律的步伐,譬如增加更多的核,驱动芯片内部的线程,以及利用各种加速器。但还是无法避免摩尔定律的更加效应已经开始放缓的事实,不断地缩小芯片的尺寸总会有物理极限:现在最新的制程工艺特色尺寸仅为7nm,而硅原子的直径为0.117nm,也便是说,在7nm工艺的芯片中的晶体管的特色尺寸仅为60个硅原子组成,随着尺寸的进一步减少,其数量还会进一步减少。

在同等面历年夜小的区域里,随着挤进越来越多的硅电路,泄电流增加、散热问题大、时钟频率增长减慢等问题难以办理。以是,有唱衰的辞吐自然不算奇怪。

这时候,有人说,Chiplet是办理摩尔定律去世亡的好方法。

什么是“Chiplet ”?

Chiplet顾名思义便是小芯片,我们可以把它想象成乐高积木的高科技版本。首先将繁芜功能进行分解,然后开拓出多种具有单一特定功能,可进行模块化组装的“小芯片”(chiplet),如实现数据存储、打算、旗子暗记处理、数据流管理等功能,并以此为根本,建立一个“小芯片”的集成系统。

大略来说,Chiplet技能便是像搭积木一样,把一些预师长西席产好的实现特定功能的芯片裸片(die)通过前辈的集成技能(比如3D integration)集成封装在一起形成一个别系芯片。而这些基本的裸片便是Chiplet。从这个意义上来说,Chiplet便是一个新的IP重用模式。未来,以Chiplet模式集成的芯片会是一个“超级”异构系统,可以带来更多的灵巧性和新的机会。

Chiplet芯片可以利用更可靠、更可靠和更便宜的技能制造。较小的硅片本身也不太随意马虎产生制造毛病。

最近,Chiplet观点热了起来,从DARPA(美国国防高等研究操持局)的CHIPS项目到Intel的Foveros,都把chiplet算作是未来芯片的主要根本技能。

Chiplet观点最早是来自DARPA的CHIPS(Common Heterogeneous Integration and IP Reuse Strategies)项目。由于最前辈的SoC并不总是能被小批量运用所接管。为了提高系统的整体灵巧性,减少下产品的设计韶光,通用的异构集成与知识产权(IP)重用策略(Chiplet)操持寻求在IP重用中建立一个新的范例。

Chiplet可以说是一种新的芯片设计模式,要实现Chiplet这种新的IP重用模式,首先要具备的技能根本便是前辈的芯片集成封装技能。SiP的观点很早就有,把多个硅片封装在一个硅片里也有良久的历史了。但要实现Chiplet这种高灵巧度,高性能,低本钱的硅片重用愿景,必须要前辈的芯片集成技能,比如3D集成技能。

Chiplet实在便是硅片级别的IP重用。设计一个别系级芯片,以前的方法是从不同的IP供应商购买一些IP,软核(代码)或硬核(版图),结合自研的模块,集成为一个SoC,然后在某个芯片工艺节点上完成芯片设计和生产的完全流程。未来,对付某些IP,你可能不须要自己做设计和生产了,而只须要买别人实现好的硅片,然后在一个封装里集成起来,形成一个SiP(System-in-Package)。以是Chiplet也可以算作一种硬核形式的IP,但它因此芯片的形式供应的。

什么是“IP ”?

IP(Intelligent Property)是具有知识产权核的集成电路的总称,是经由反复验证过的、具有特定功能的宏模块,可以移植到不同的半导体工艺中。到了SoC阶段,IP核设计已成为ASIC电路设计公司和FPGA供应商的主要任务,也是实在力的表示。对付FPGA开拓软件,其供应的IP核越丰富,用户的设计就越方便,其市场占用率就越高。目前,IP核已经变成SoC系统设计的基本单元,并作为独立设计成果被交流、转让和发卖。

IP(Intellectual Property)核对应描述功能行为的不同分为三类,即软核(Soft IP Core)、固核(Firm IP Core)和硬核(Hard IP Core)。

1.软核

软核在EDA设计领域指的是综合之前的寄存器传输级(RTL)模型;详细在FPGA设计中指的是对电路的硬件措辞描述,包括逻辑描述、网表和帮助文档等。软核只经由功能仿真,须要经由综合以及布局布线才能利用。其优点是灵巧性高、可移植性强,许可用户自配置;缺陷是对模块的预测性较低,在后续设计中存在发生缺点的可能性,有一定的设计风险。软核是IP核运用最广泛的形式。IP软核常日是用HDL文本形式提交给用户,它经由RTL级设计优化和功能验证,但个中不含有任何详细的物理信息。据此,用户可以综合出精确的门电路级设计网表,并可以进行后续的构造设计,具有很大的灵巧性,借助于EDA综合工具可以很随意马虎地与其他外部逻辑电路合成一体,根据各种不同半导体工艺,设计成具有不同性能的器件。软IP内核也称为虚拟组件(VC-Virtual Component)。

2.固核

固核在EDA设计领域指的是带有平面方案信息的网表;详细在FPGA设计中可以看做带有布局方案的软核,常日以RTL代码和对应详细工艺网表的稠浊形式供应。将RTL描述结合详细标准单元库进行综合优化设计,形成门级网表,再通过布局布线工具即可利用。和软核比较,固核的设计灵巧性稍差,但在可靠性上有较大提高。目前,固核也是IP核的主流形式之一。IP固核的设计程度则是介于软核和硬核之间,除了完成软核所有的设计外,还完成了门级电路综合和时序仿真等设计环节。一样平常以门级电路网表的形式供应给用户。

3.硬核

硬核在EDA设计领域指经由验证的设计版图;详细在FPGA设计中指布局和工艺固定、经由前端和后端验证的设计,设计职员不能对其修正。不能修正的缘故原由有两个:首先是系统设计对各个模块的时序哀求很严格,不许可打乱已有的物理版图;其次是保护知识产权的哀求,不许可设计职员对其有任何改动。IP硬核的不许修正特点使其复用有一定的困难,因此只能用于某些特定运用,利用范围较窄。IP硬核是基于半导体工艺的物理设计,已有固定的拓扑布局和详细工艺,并已经由工艺验证,具有可担保的性能。其供应给用户的形式是电路物理构造掩模版图和全套工艺文件,是可以拿来就用的全套技能。

IP核的供应办法上,常日将其分为软核、硬核和固核这3类。从完成IP核所花费的成本来讲,硬核代价最大;从利用灵巧性来讲,软核的可复用利用性最高。

当硬核因此硅片的形式供应时,就变成了Chiplet。

什么是“SiP ”?

SiP(System-in Package)系统级封装是将多种功能芯片,包括处理器、存储器、FPGA等功能芯片集成在一个封装内,从而实现一个基本完全的功能。与SoC(System on Chip系统级芯片)相对应。不同的是系统级封装是采取不同芯片进行并排或叠加的封装办法,而SoC则是高度集成的芯片产品。

SiP可定义为:将多个具有不同功能的有源电子元件与可选无源器件,以及诸如MEMS或者光学器件等其他器件优先组装到一起,实现一定功能的单个标准封装件,从而形成一个别系或者子系统。

SiP中的IC芯片可以垂直堆叠或水平排列,一个SiP中可以包含很多种芯片,如专门的处理器,DRAM,Flash 等,结合被动元件电阻、电容、电感等都可以封装在同一个SiP中,这意味着一个完全的系统功能单元可以在SiP封装中建立。

SiP办理方案须要多种封装技能,如引线键合、倒装芯片、芯片堆叠、基板腔体、基板集成RF器件、埋入式电阻\电容\电感、硅通孔TSV,圆片级封装等。SiP 是超越摩尔定律的主要实现路径。

摩尔定律,Chiplet,IP,SiP之间的关联

摩尔定律逐渐失落效之后的日子便被称为“后摩尔定律时期”。所谓后摩尔定律时期,便是业者不再以追求更大效能的芯片为紧张目的,而是强调多元化与实用性的原则。也便是说,产品能发挥实际效用便是最好的质量,也是最具经济代价的东西。

DARPA的CHIPS(通用异构整合和IP重用策略)操持赢得了波音、洛克希德、诺斯洛普·格鲁门、英特尔、美光、Cadence、Synopsys等公司的支持,用于商业和军事/航空运用。同样,SEMI和IEEE也在推广更快整合的共同路线图,西门子的Mentor奇迹部已经建立了一个可以在这方面供应帮助的SiP封装流程。

在此根本上,须要开拓工具和方法,使所有这些都能发挥浸染。虽然较小的芯片比较于较大的芯片有更好的产量,但当这些芯片被封装在一起时,有许多事情可能会出错。一个坏的Chiplet会杀去世全体SiP封装内的系统。此外,芯片或模组在封装、测试乃至运输过程中都可能受到破坏,如果涉及多个芯片,则破坏的本钱会更高。

未来的电脑系统可能只包含一个CPU芯片(chiplet)和几个GPU,这些GPU都连接到这个Chiplet芯片上,形成芯片网络,组成系统。

末了总结一句话:

在后摩尔定律时期,IP硬核会逐渐芯片化,形成Chiplet,然后以SiP的形式封装形成系统,使得摩尔定律连续延续下去,这也是摩尔定律的一次革命。

免责声明:本文由作者原创。文章内容系作者个人不雅观点,半导体行业不雅观察转载仅为了传达一种不同的不雅观点,不代表半导体行业不雅观察对该不雅观点赞许或支持,如果有任何异议,欢迎联系半导体行业不雅观察。

本日是《半导体行业不雅观察》为您分享的第2221期内容,欢迎关注。

★存储,江湖

★TWS蓝牙芯片的新变局

★德州仪器再关闭两座晶圆厂,冰火两重天市场局势突显

“芯”系疫情|AI|英伟达|华为|晶圆|CMOS|射频|2020半导体市场